(LUẬN VĂN THẠC SĨ) Xử lý tín hiệu thời gian thực bằng phương pháp số trên môi trường phát triển ứng dụng DSP56307EVM áp dụng trong các hệ định vị vô tuyến

139

4

0

THÔNG TIN TÀI LIỆU

Thông tin cơ bản

| Tiêu đề | Xử lý tín hiệu thời gian thực bằng phương pháp số trên môi trường phát triển ứng dụng DSP56307EVM áp dụng trong các hệ định vị vô tuyến |

|---|---|

| Tác giả | Lê Hồng Hà |

| Người hướng dẫn | TS. Bạch Gia Dương |

| Trường học | Đại học Quốc gia Hà Nội |

| Chuyên ngành | Công nghệ điện tử - viễn thông |

| Thể loại | luận văn thạc sĩ |

| Năm xuất bản | 2008 |

| Thành phố | Hà Nội |

| Định dạng | |

|---|---|

| Số trang | 139 |

| Dung lượng | 4,41 MB |

Nội dung

Ngày đăng: 28/06/2022, 05:02

HÌNH ẢNH LIÊN QUAN

TỪ KHÓA LIÊN QUAN

TRÍCH ĐOẠN

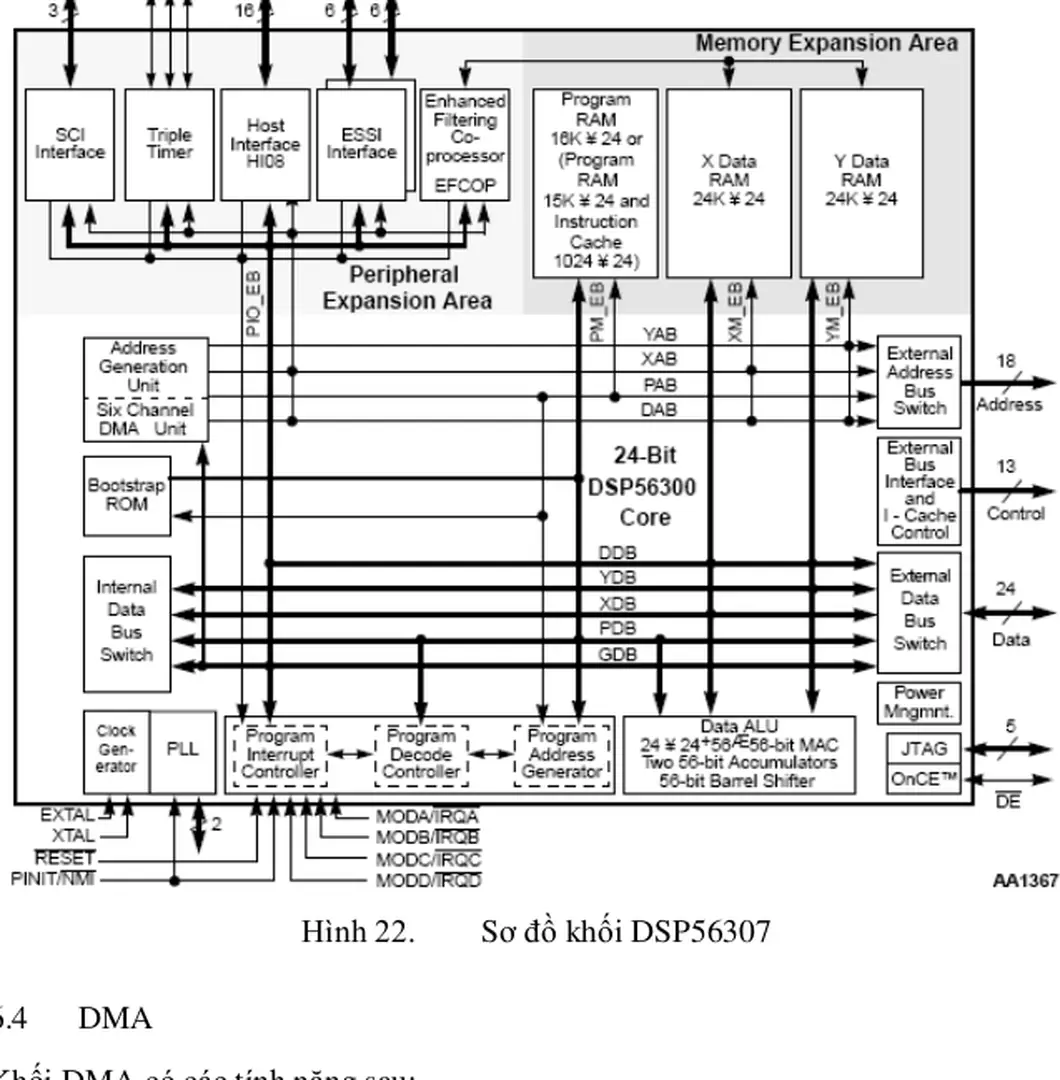

Các khối chức năng của Core DSP56300

Các thanh ghi của EFCOP

Sơ đồ chân vi xử lý DSP56307 Codec âm thanh CS4218-KQ [3, 5] Bộ chuyển đổi lệnh Giao diện truyền tin nối tiếp (SCI) Thực hiện lọc sử dụng phương pháp tích luỹ Nâng cao tốc độ lấy mẫuTÀI LIỆU CÙNG NGƯỜI DÙNG

-

114 1 0

-

108 3 0

-

116 3 0

TÀI LIỆU LIÊN QUAN

-

2 10 0

-

2 150 0

-

12 193 0

-

12 273 1

-

139 2 0

-

95 57 0

-

35 546 2

-

132 31 0