Models in Hardware Testing- P2 pot

Models in Hardware Testing- P2 pot

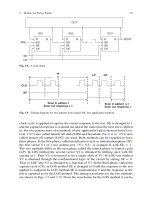

... Patterns generating a floating line voltage interpreted as logic 1 on the tester are plotted in dotted lines, whereas patterns generating a logic 0 in the floating line are plotted in plain lines. To ... Assuming an interconnect full open defect, if an intermediate voltage is induced on the floating line, the two transistors driven by the floating line may be in a conduction state, genera...

Ngày tải lên: 02/07/2014, 15:20

Models in Hardware Testing- P4 pot

... between line b and line f of the circuit and any path fault containing the two lines is untestable. The lines b and f are logical lines which are physical lines with which a rising or falling transition ... inputs and circuit outputs. 90 S.M. Reddy Inputs Outputs f-line f-line b-line l b-line Decision point FFR backward expansion line forward expansion line initial PP I Fig. 3.19 Step-wise pa...

Ngày tải lên: 02/07/2014, 15:20

Models in Hardware Testing- P6 potx

... Torino, Italy e-mail: stefano.dicarlo@polito.it H J. Wunderlich (ed.), Models in Hardware Testing: Lecture Notes of the Forum in Honor of Christian Landrault, Frontiers in Electronic Testing ... Nabdominates a & a AND-dominates b 1abdominates a & a OR-dominates b N b Na wired-AND N babAND-dominates a & a OR-dominates b bawired-OR All common bridge fault models are pres...

Ngày tải lên: 02/07/2014, 15:20

Models in Hardware Testing: Lecture Notes of the Forum in Honor of Christian Landrault docx

... Patterns generating a floating line voltage interpreted as logic 1 on the tester are plotted in dotted lines, whereas patterns generating a logic 0 in the floating line are plotted in plain lines. To ... of the gate leakage currents in uencing the downstream gate, the steady state voltage of the floating line can be predicted. Assuming a float- ing line driving an inverter for a 90 nm tech...

Ngày tải lên: 27/06/2014, 00:20

Models in Hardware Testing- P1 pptx

... the floating line is driving an inverter. 1 Open Defects in Nanometer Technologies 5 c. The third factor in uencing the floating line voltage is the trapped charge accumulated in the floating structure ... spent together discussing, eating, tasting wine, talking of culture, sharing everyday problems of our private lives, telling us your experiences in fishing and hunting, have been invalua...

Ngày tải lên: 02/07/2014, 15:20

Models in Hardware Testing- P5 pps

... 1]1/0). Propagation through the inverting NAND gate F with non-controlling value 1 at its first input results in one more inversion of the interval, yielding the original ADI [0, R 0 E ] at line w. The XOR gate ... created at all lines involved in at least one sim- ulated RBF. The FSICs of the gates driving the bridged lines are determined by good-simulation. The masks are filled by looking...

Ngày tải lên: 02/07/2014, 15:20

Models in Hardware Testing- P7 ppt

... physical design constraints can be included in the reordering algorithm (Bonhomme et al. 2003). 7.5.1.3 Logic Insertion in Scan Chain This technique consists in inserting logic elements (XOR ... cells in the scan chains implies a change of the bit order in each test vector to preserve the initial fault coverage. Finding the best (less power consuming) order of scan cells in the sc...

Ngày tải lên: 02/07/2014, 15:20

Models in Hardware Testing- P8 ppt

... considerations in this technique will consist in modify- ing the initial selective encoding procedure by using one of the following X-filling heuristics to fill don’t-care bits: 0-filling: all Xs in the ... testing: off-line testing with respect to manufacturing defects and on-line testing mechanisms to cope with faults occurring during normal operation (Section 8.2), and a recursive for...

Ngày tải lên: 02/07/2014, 15:20

Models in Hardware Testing- P9 pptx

... errors induced in the main registers was found to be less than 1% in the experiments reported in Johansson (1994). 8.3.2.2 Pin-Level Fault Injection The experiments with the pin-level fault injection ... Principle of pin-forcing fault injection Fig. 8.13 Application of electromagnetic interferences It is noteworthy that the pins of the ICs connected, by means of an equipotential line, t...

Ngày tải lên: 02/07/2014, 15:20

Friction and Lubrication in Mechanical Design P2 pot

... Misharin, J. A., “Influence of the Friction Conditions on the Magnitude of the Friction Coefficient in the Case of Rolling with Sliding,” International Conference on Gearing, Proceedings, ... given by Boussinesq [I] as: 22 Introduction 15 (ascending) region, and the thermal (descending) region. At low sliding speeds a linear relation exists, the slope of which defines a quasi...

Ngày tải lên: 04/07/2014, 14:20