Bài giảng Thiết kế mạch số dùng HDL - Chương 4: Thiết kế luận lý với Verilog có nội dung trình bày giới thiệu về HDLs và verilog; mô hình cấu trúc cho mạch luận lý tổ hợp; Mô phỏng luận lý, kiểm chứng thiết kế và phương pháp luận kiểm tra; thời gian trễ truyền lan;... Mời các bạn cùng tham khảo!

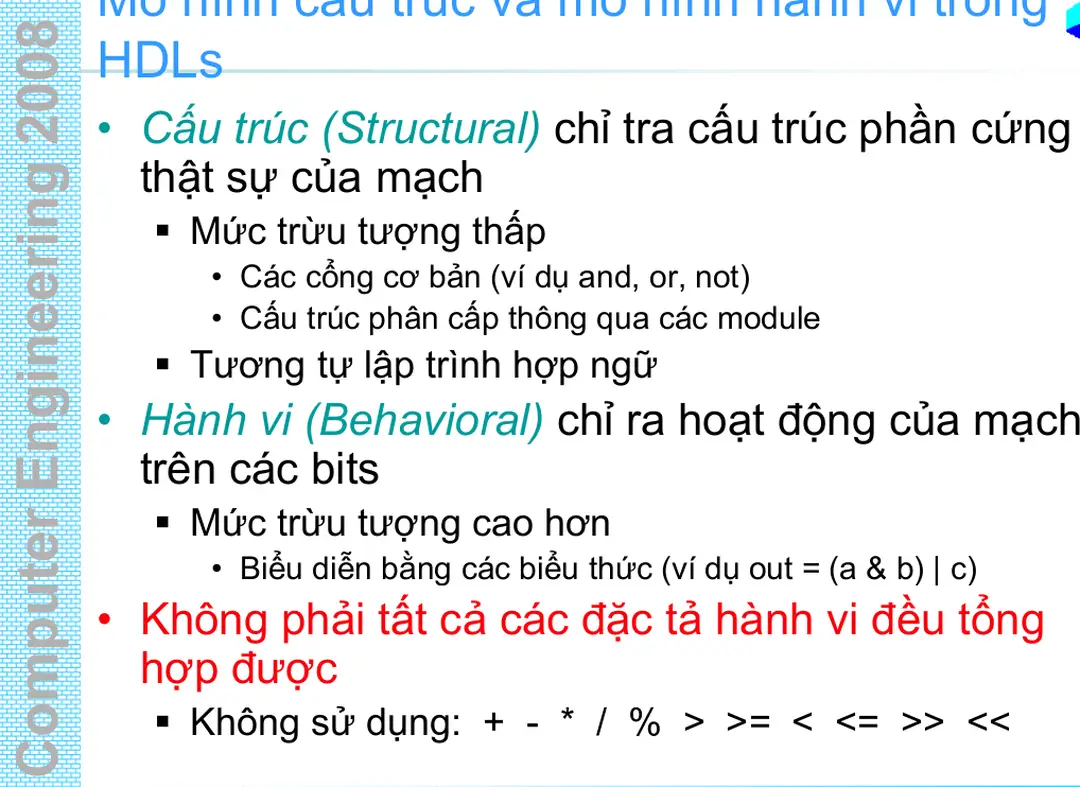

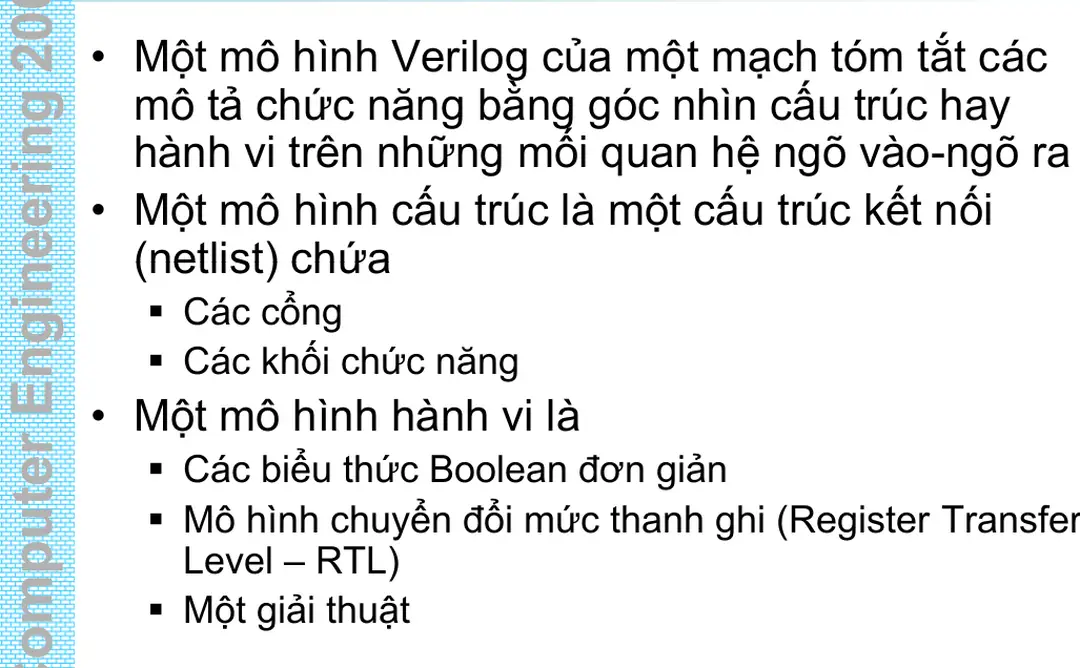

dce 2008 Thiết kế mạch số với HDL Chương 4: Thiết kế luận lý với g Verilog Co omputer E Engineerin ng 20 008 Nội dung • Giới thiệu HDLs verilog • Mơ hình cấu trúc cho mạch luận lý tổ hợp • Mơ luận lý, kiểm chứng thiết kế ph ơng pháp lluận phương ận kiểm tra • Thời gian trễ truyền lan • Mơ hình bảng thật cho mạch luận lý tổ hợp với Verilog Advanced Digital Design with the Verilog HDL – chapter ©2008, Pham Quoc Cuong Co omputer E Engineerin ng 20 008 Nội dung • Giới thiệu HDLs verilog • Mơ hình cấu trúc cho mạch luận lý tổ hợp • Mô luận lý, kiểm chứng thiết kế ph ơng pháp lluận phương ận kiểm tra • Thời gian trễ truyền lan • Mơ hình bảng thật cho mạch luận lý tổ hợp với Verilog Advanced Digital Design with the Verilog HDL – chapter ©2008, Pham Quoc Cuong Co omputer E Engineerin ng 20 008 Giới thiệu HDLs • HDLs (Hardware Description Languages) Khơng ngơn ngữ lập trình Tựa C Thêm chức mơ hình hóa hóa, mơ chức Verilog vs vs VHDL • Các bước thiết kế HDL Mô tả mạch từ khóa Biên dịch để kiểm tra cú pháp (syntax) Mô hỏ để kiểm kiể tra t chức ă ủ mạch h Advanced Digital Design with the Verilog HDL – chapter ©2008, Pham Quoc Cuong Co omputer E Engineerin ng 20 008 Phương pháp luận thiết kế HDL Đặc tả HDL Mô Kiểm tra: thiết kế yêu cầu chưa? Chức năng: Hành vi I/O Mức ghil (Kiến trúcl) Mức luận lý (Cổng) Mức transistor (Điển tử) Timing: Waveform Behavior Advanced Digital Design with the Verilog HDL – chapter Cấu trúc/hành vi mạch Tổng hợp Ánh xạ đặc tả thành thực ©2008, Pham Quoc Cuong Co omputer E Engineerin ng 20 008 Mô hình cấu trúc mơ hình hành vi HDLs • Cấu trúc (Structural) tra cấu trúc phần cứng thật mạch Mức trừu tượng thấp ấ • Các cổng (ví dụ and, or, not) • Cấu trúc phân cấp thông qua module Tương tự lập trình hợp ngữ • Hành vi (Behavioral) hoạt động mạch t ê bit bits Mức trừu tượng cao • Biểu diễn g biểu thức ((ví dụ ụ out = ((a & b)) | c)) • Khơng phải tất đặc tả hành vi tổng hợp Không sử dụng: + - * / % > >= < > Điều khiển trễ truyền Các phát biểu phía sau phải đợi Advanced Digital Design with the Verilog HDL – chapter ©2008, Pham Quoc Cuong 30 Co omputer E Engineerin ng 20 008 Khuôn mẫu cho testbench module t_module (); reg …; wire …; parameter time_out = 100; UUT_name U1 (port_list); initial $ $monitor(); (); initial #time_out $finish initial begin … end Tên module UUT Khai báo kiểu ghi để chứa giá trị cho biến ngõ vào UUT Khai báo kiểu wire cho ngõ UUT Khai báo tham số Tín hiệu Tí hiệ đ xuất ất dạng d text t t Kết thúc mô sau thời gian time_out Xây dựng tín hiệu ngõ vào cho U1 endmodule Advanced Digital Design with the Verilog HDL – chapter ©2008, Pham Quoc Cuong 31 Co omputer E Engineerin ng 20 008 Ví dụ Advanced Digital Design with the Verilog HDL – chapter ©2008, Pham Quoc Cuong 32 Co omputer E Engineerin ng 20 008 Kích thước số • Chỉ số lượng bit dùng để lưu trữ số u _o of_b bit> ‘ base a ue •Bài giảng Thiết kế mạch số dùng HDL - Chương 4: Thiết kế luận lý với Verilog

39

5

0

THÔNG TIN TÀI LIỆU

Thông tin cơ bản

| Tiêu đề | Thiết Kế Luận Lý Với Verilog |

|---|---|

| Tác giả | Pham Quoc Cuong |

| Trường học | Computer Engineering |

| Thể loại | lecture |

| Năm xuất bản | 2008 |

| Định dạng | |

|---|---|

| Số trang | 39 |

| Dung lượng | 429,17 KB |

Nội dung

Ngày đăng: 05/07/2022, 14:19

HÌNH ẢNH LIÊN QUAN

TỪ KHÓA LIÊN QUAN

TÀI LIỆU CÙNG NGƯỜI DÙNG

-

8 32 0

-

43 86 0

-

115 4 0

-

188 7 0

-

45 8 0

-

46 4 0

TÀI LIỆU LIÊN QUAN

-

50 3 0

-

33 187 0

-

73 339 1

-

82 562 12

-

16 193 0

-

20 273 2

-

50 893 0

-

28 239 0