circuit design with vhdl pedroni 2nd edition

Circuit design with VHDL (vietnamese ver )

... viết mã VHDL. Mã VHDL này sẽ được lưu vào file có đuôi là .vhd và có tên cùng với tên thực thể. Mã VHDL sẽ được mô tả ở tầng chuyển đổi thanh ghi. Hình 1.1. Tóm tắt quy trình thiết kế VHDL - ... đưa ra tiêu chuẩn về VHDL( tiêu chuẩn IEEE-1076-1987). VHDL được phát triển để giải quyết các khó khăn trong việc phát triển, thay đổi và lập tài liệu cho các hệ thống số. VHDL là một ngôn ngữ ... cứng khác ta thấy VHDL có một số ưu điểm hơn hẳn là: - Thứ nhất là tính công cộng: VHDL được phát triển dưới sự bảo trợ của chính phủ Mỹ và hiện nay là một tiêu chuẩn của IEEE. VHDL được sự hỗ

Ngày tải lên: 24/03/2014, 23:28

fundamentals of rf circuit design with low noise oscillators

... Fundamentals of RF Circuit Design with Low Noise Oscillators Jeremy Everard Copyright © 2001 John Wiley & Sons Ltd ISBNs: ... Equivalent circuit device models are critical for the accurate design and modelling of RF components including transistors, diodes, resistors, capacitors and inductors This chapter will begin with ... between them for easier circuit manipulation It also offers improved insight As an example S21 for a bipolar transistor, with an fT of 5GHz, will be calculated and compared with the data sheet values

Ngày tải lên: 24/08/2014, 17:20

University physics with modern physics 2nd edition bauer test bank

... 61.3 kg starts from rest and accelerates with a constant acceleration of 1.07 m/s2 until she reaches a velocity of 8.1 m/s She then continues running with this constant velocity How far has she ... Straight Line 61 A ball is thrown directly down from the top of a building with a speed of 12 m/s, and it lands on the ground with a velocity times the initial velocity How high is the building (in ... Motion in a Straight Line 18 A car moving along the x direction has acceleration, ax that varies with time as shown in the figure At the moment, t = s, the car is located at x = 12 m and has a

Ngày tải lên: 18/11/2017, 09:03

Appication specific hardware architecture design with VHDL

... Architecture Design with VHDL Signals and Communication Technology More information about this series at http://www.springer.com/series/4748 Bogdan Belean Application-Specific Hardware Architecture Design ... Introduction to Digital Design with VHDL 1.1 Digital Systems—Introductory Notes 1.2 Levels of Abstraction 1.3 The VHDL Hardware Description ... Concurrent VHDL Code 1.4.2 Sequential VHDL Code 1.5 Structural Description with VHDL 1.6 VHDL Code for Simulation Test-Benches 1.7 Finite

Ngày tải lên: 22/01/2018, 16:46

Solutions manual for university physics with modern physics 2nd edition by bauer and westfall

... https://getbooksolutions.com/download/test-bank-for-university-physics -with- modern-physics -2nd- edition- by-bauer-a download Solutions manual: https://getbooksolutions.com/download/solutions-manual-for-university-physics -with- modern-physics -2nd- editi LinkLink ... Solutions Manual for University Physics with Modern Physics 2nd Edition by Wolfgang Bauer and Gary D.Westfall Chapter 2: Motion in a Straight Line Link ... +1 s | x(t ) − x(t1 ) | s= , with t = s and t1 = −1 s t − t1 (b) The average velocity is given by the total displacement over the time interval x(t ) − x(t1 ) , with t = s and t1 = −5 s v= t

Ngày tải lên: 28/02/2019, 15:47

Link full download test bank for university physics with modern physics 2nd edition by bauer and westfall

... Test Bank for University Physics with Modern Physics 2nd Edition by Wolfgang Bauer and Gary D Westfall Chapter 02 Motion in a Straight Line Multiple ... is fired through a board, 8.00 cm thick, with its line of motion perpendicular to the face of the board If it enters with a speed of 300 m/s and emerges with a speed of 100 m/s, the bullet's acceleration ... 61.3 kg starts from rest and accelerates with a constant acceleration of 1.07 m/s2 until she reaches a velocity of 8.1 m/s She then continues running with this constant velocity How far has she

Ngày tải lên: 02/03/2019, 09:19

Test bank for university physics with modern physics 2nd edition by bauer

... Question Section: 01.03 Test Bank for University Physics with Modern Physics 2nd Edition by Bauer 56 A cube with a volume of V consists of faces each with an area of A If the area of each face is increased ... for University Physics with Modern Physics 2nd Edition by Bauer 16 The surface area of a window pane of length 20.5 cm and width 11.9 cm is (given in scientific notation and with the correct number ... 01 #15 Test Bank for University Physics with Modern Physics 2nd Edition by Bauer more difficult Multiple Choice Question Section: 01.06 22 The answer with correct number of significant figures

Ngày tải lên: 31/08/2020, 10:25

operational amplifier speed and accuracy improvement analog circuit design with structural methodology pdf

... =1 ¦ Gk−1 ) −1 ¦ ik n n ¦ ik if ¦ G −k k =1 and Power circuits with ideal source Measurements with ideal instruments zs → ∞ Input circuits with ideal instruments or sources −1 i Lk = z Lk (1 + ... Analysis and design of analog integrated circuits, New York: Wiley, 1993 10 J H Huijsing, Operational amplifiers, Dordrecht, The Netherlands: Kluwer, 2001 11 J Williams, ed., Analog circuit design, ... MOS cascode bias circuit for all current levels”, Proc ISCAS2002, vol 3, pp 619-622, Phoenix, AZ, May 26-29, 2002 32 E Seevinck, “CMOS translinear circuits” in Analog Circuit Design, Dordrecht,

Ngày tải lên: 20/10/2021, 21:42

Designing with the mind in mind simple guide to understanding user interface design guidelines 2nd edition

... Designing with the Mind in Mind Simple Guide to Understanding User Interface Design Guidelines Second Edition This page intentionally left blank Designing with the Mind in ... disabilities: An introduction, SAP Design Guild Retrieved from, http://www.sapdesignguild.org/editions/highlight_articles_01/vision_physiology.asp Ware, C., 2008 Visual thinking for design Morgan Kaufmann, ... interaction design (e.g., the design of the workflow for a smartphone to record diet), and the third, perhaps a little overly grandly, interaction science (e.g., the use of Fitts’ law to design button

Ngày tải lên: 02/03/2019, 10:32

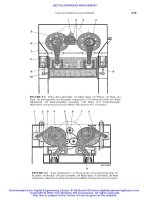

handbook of die design 2nd edition phần 1 ppsx

... 10 :28 AM Page 31 BASIC DIE DESIGN AND DIE- WORK INFLUENCING FACTORS 31 BASIC DIE DESIGN AND DIE- WORK INFLUENCING FACTORS TABLE 1- 1 Corner Bead Design Data In inches: H M (ref) ... DIE DESIGN AND DIE- WORK INFLUENCING FACTORS BASIC DIE DESIGN AND DIE- WORK INFLUENCING FACTORS 33 FIGURE 1- 36 Circumferential ribs in stampings (From Frank W Wilson, Die Design ... provide the...Suchy_CH 01. qxd 11 /08/05 10 :28 AM Page 9 BASIC DIE DESIGN AND DIE- WORK INFLUENCING FACTORS BASIC DIE DESIGN AND DIE- WORK INFLUENCING FACTORS FIGURE 1- 12 9 Side view

Ngày tải lên: 08/08/2014, 13:20

handbook of die design 2nd edition phần 2 pptx

... materials are capable of withstanding high temperatures at extended periods of time For that reason, the tooling with selectively cooled portions is sometimes being used along with heat-resistant ... bring a part to size, or a drawn shell within the drawing dimensions by striking it without allowing for its walls to become thinner Horn dies are equipped with a horn, which is a sort of protruding ... discharged over a spark gap located in a tank with water This creates a sudden release of steam, which, along with ionization, creates a high pressure shock wave within the liquid The die, containing

Ngày tải lên: 08/08/2014, 13:20

handbook of die design 2nd edition phần 3 docx

... 4-14; a tapered and counterbored relief with a die life (also called “land”), and a relief that is tapered through with no die life Each of these designs has its advantages and disadvantages ... material, either in pieces or encapsulated, is placed in a water-filled tank alongside or within a die with the material to be formed. The charge, when detonated, prompts release of a great amount ... movement of metal layers with respect to each other. This aids the forming process and improves homogeneity of the outcome. The speed of the forming is increased as well, with lessened friction

Ngày tải lên: 08/08/2014, 13:20

handbook of die design 2nd edition phần 4 pps

... further divided into presses with a single column, double column, and pillar-supported presses (Fig. 5-7). 216 CHAPTER FIVE FIGURE 5-4 Double-column press. (Reprinted with permission from Müller ... unfavorably the gap-frame presses equipped with tie rods is the misalignment caused by the tie rods themselves. These connecting links, in order to provide the press with the stability and resistance ... C-frame presses or gap-frame • Closed-frame presses or O-frame C-frame construction is often used with smaller-capacity presses. Their main advantage lies in the easily accessible work area, which

Ngày tải lên: 08/08/2014, 13:20

handbook of die design 2nd edition phần 5 pot

... hard metals, with dependence on the modulus of elasticity (also called Young Modulus) of a particular material The amount of springback increases with greater yield strength or with the material’s ... using small bend radii Equation (8-14) was proved true for bends with large bend radii or for those with small bend angles However, with small bend radii, it may be considered valid only if the ... emphasized with time and may cause the part’s collapse and perhaps total destruction Both residual stresses and springback can bring about a host of unexpected problems and a sound part design, along with

Ngày tải lên: 08/08/2014, 13:20

handbook of die design 2nd edition phần 6 docx

... factors and blank dimensions for deep drawing with single- and double-action dies (From: Frank W Wilson, Die Design Handbook, New York, 1 965 Reprinted with permission from ... as shown in Fig. 8-48, is an extension of the curved or linear portion, connecting with another line sharply, with no radius applied (see detail “P”). Round recesses can be assessed from Table ... From this relationship, other values may be assessed with the use of the formula (8-18) where all values are as shown in Fig. 8-50. However, with the bend radius being too small, the value a of

Ngày tải lên: 08/08/2014, 13:20

Tài liệu Circuit design with VHDL ppt

... Cataloging-in-Publication Data Pedroni, Volnei A. Circuit design with VHDL/ Volnei A. Pedroni. p. cm. Includes bibliographical references and index. ISBN 0-262-16224-5 (alk. paper) 1. VHDL (Computer hardware ... Altera Quartus II Tutorial 343 Appendix E: VHDL Reserved Words 355 Bibliography 357 Index 359 x Contents TLFeBOOK with VHDL Volnei A. Pedroni Circuit Design TLFeBOOK To Claudia, Patricia, Bruno, ... another. While books on VHDL give limited emphasis to digital design concepts, and books on digital design discuss VHDL only briefly, the present work completely integrates them. It is indeed a design- oriented...

Ngày tải lên: 12/12/2013, 11:16

Circuit Design with VHDL pptx

... THEN d clk rst q DFF Figure 2.5 DFF with asynchronous reset. 18 Chapter 2 TLFeBOOK with VHDL Volnei A. Pedroni Circuit Design Circuit Design with VHDL Volnei A. Pedroni This textbook teaches VHDL using system ... Cataloging-in-Publication Data Pedroni, Volnei A. Circuit design with VHDL/ Volnei A. Pedroni. p. cm. Includes bibliographical references and index. ISBN 0-262-16224-5 (alk. paper) 1. VHDL (Computer hardware ... Massachusetts 02142 http://mitpress.mit.edu 0-262-16224-5 ,!7IA2G2-bgcceb!:t;K;k;K;k Circuit Design with VHDL Pedroni 46183Pedroninew 2004-10-11 14:06 Page 1 TLFeBOOK Additionally, four appendices on...

Ngày tải lên: 19/03/2014, 21:20

Fundamentals of RF Circuit Design With Low Noise Oscillators

... RF Circuit Design with Low Noise Oscillators. Jeremy Everard Copyright © 2001 John Wiley & Sons Ltd ISBNs: 0-471-49793-2 (Hardback); 0-470-84175-3 (Electronic) 14 Fundamentals of RF Circuit ... 1800MHz and 7.6GHz. These oscillator designs show very close correlation with the theory usually within 2dB of the predicted minimum. It also includes a detailed design example. The chapter then ... amplifier design and includes Load Pull measurement and design techniques and a more analytic design example of a broadband, efficient amplifier operating from 130 to 180 MHz. The design example...

Ngày tải lên: 08/04/2013, 10:50

Tài liệu Logic Design with VHDL doc

... 1 0 1 10 1 0 10 01 00 11 10 A BC C B A F A F = AB' + BC + AC (c) Network with hazard removed C E B A D F 0 1 0 1 10 1 0 10 01 00 11 10 A BC F = AB' + BC 1 - Hazard (a) Network with 1-hazard B D E F 0 ns 10 ns 20 ns 30 ... inversion Figure 1-7 Conversion to NOR Gates (a) AND-OR network (b) Equivalent NOR-gate network 8 VHDL Processes General form of Process process(sensitivity-list) begin sequential-statements end ... (X) Outputs (Z) clock State Figure 1-16 General Model of Mealy Sequential Machine 4 Figure 2-2 VHDL Program Structure Entity Architecture Entity Architecture Module 1 Entity Architecture Module...

Ngày tải lên: 12/12/2013, 09:16

Tài liệu Web Database Applications with PHP & MySQL, 2nd Edition ppt

... applica- WebDatabaseApplications with PHP and MySQL Downloa d f r o m W o w ! e B o o k < w w w.woweb o o k . c o m > This is the Title of the Book, eMatter Edition Copyright â 2007 O’Reilly ... Client in the Three-Tier Model Given that a web database application built with a three-tier architecture doesn’t fit naturally with HTTP, why use that model at all? The answer mostly lies in the popu- larity ... unfamiliar with the web environment and its underly- ing protocols. Appendix E is a brief introduction to entity-relationship modeling for databases and shows the steps we took in designing the...

Ngày tải lên: 15/02/2014, 16:20

Bạn có muốn tìm thêm với từ khóa: