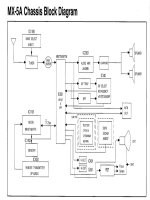

pwm module block diagram one output pair independent mode

Tài liệu Power Supply Block Diagram ppt

- 53

- 403

- 1

ZO3 SYSTEM BLOCK DIAGRAM potx

- 28

- 422

- 0

A3 BLOCK DIAGRAM doc

- 56

- 333

- 0

A6Jc/m Block Diagram docx

- 64

- 346

- 0

A6K BLOCK DIAGRAM potx

- 64

- 350

- 0

Yonah/RC410MD/IXP450 BLOCK DIAGRAM pptx

- 50

- 309

- 0

Function Block Diagram (FBD) for S7-300 and S7-400 Programming pps

- 221

- 1.2K

- 1

Tài liệu Báo cáo khoa học: "Using Error-Correcting Output Codes with Model-Refinement to Boost Centroid Text Classifier" ppt

- 4

- 461

- 0

hand gesture recognition using input-output hidden markov models

- 6

- 421

- 0

Tài liệu CopperTen® Augmented Category 6 8-Pair Block ppt

- 2

- 177

- 0

BUSINESS ENGLISH & LETTER WRITING STUDY GUIDE FOR MODULE ONE pptx

- 40

- 1.3K

- 2

Báo cáo khoa học: "A comparison of clausal coordinate ellipsis in Estonian and German: Remarkably similar elision rules allow a language-independent ellipsis-generation module" pot

- 4

- 321

- 0

4.5 V TO 20 V INPUT, 3 A OUTPUT SYNCHRONOUS PWM SWITCHER WITH INTEGRATED FET (SWIFT) doc

- 28

- 340

- 0

3 V TO 6 V INPUT, 1.5 A OUTPUT SYNCHRONOUS BUCK PWM SWITCHER WITH INTEGRATED FETs (SWIFT) pptx

- 21

- 347

- 0

Module III Scanning.Scanning - DefinitionScanning is one of the three components of intelligence ppsx

- 74

- 332

- 0

Using UML part one structural modeling diagram

- 26

- 312

- 0